Most of the world’s most superior digital methods—together with Internet routers, wireless base stations, medical imaging scanners, and some artificial intelligence tools—depend upon field-programmable gate arrays. Computer chips with inner {hardware} circuits, the FPGAs will be reconfigured after manufacturing.

On 12 March, an IEEE Milestone plaque recognizing the primary FPGA was devoted on the Advanced Micro Devices campus in San Jose, Calif., the previous Xilinx headquarters and the birthplace of the know-how.

The FPGA earned the Milestone designation as a result of it launched iteration to semiconductor design. Engineers might redesign {hardware} repeatedly with out fabricating a brand new chip, dramatically lowering growth threat and enabling quicker innovation at a time when semiconductor prices had been rising quickly.

The ceremony, which was organized by the IEEE Santa Clara Valley Section, introduced collectively professionals from throughout the semiconductor industry and IEEE management. Audio system on the occasion included Stephen Trimberger, an IEEE and ACM Fellowwhose technical contributions helped shape modern FPGA architecture. Trimberger reflected on how the invention enabled software-programmable hardware.

Solving computing’s flexibility-performance tradeoff

FPGAs emerged in the 1980s to address a core limitation in computing. A microprocessor executes software program directions sequentially, making it versatile however generally too sluggish for workloads requiring many operations directly.

On the different excessive, application-specific integrated circuits are chips designed to do just one job. ASICs obtain excessive effectivity however require prolonged growth cycles and nonrecurring engineering prices, that are massive, upfront investments. Bills embody designing the chip and getting ready it for manufacturing—a course of that entails creating detailed layouts, constructing masks for the fabrication machines, and organising manufacturing strains to deal with the tiny circuits.

“ASICs can ship the perfect efficiency, however the growth cycle is lengthy and the nonrecurring engineering price will be very excessive,” says Jason Cong, an IEEE Fellow and professor of laptop science on the University of California, Los Angeles. “FPGAs present a candy spot between processors and customized silicon.”

Cong’s foundational work in FPGA design automation and high-level synthesis reworked how reconfigurable methods are programmed. He developed synthesis instruments that translate C/C++ into {hardware} designs, for instance.

On the coronary heart of his work is an underlying precept first espoused by electrical engineer Ross Freeman: By configuring {hardware} utilizing programmable reminiscence embedded contained in the chip, FPGAs mix hardware-level pace with the adaptability historically related to software program.

The FPGA structure originated within the mid-Eighties at Xilinx, a Silicon Valley firm based in 1984. The invention is broadly credited to Freeman, a Xilinx cofounder and the startup’s CTO. He envisioned a chip with circuitry that may very well be configured after fabrication quite than mounted completely throughout creation.

Articles in regards to the history of the FPGA emphasize that he noticed it as a deliberate break from standard chip design.

On the time, semiconductor engineers handled transistors as scarce sources. Customized chips had been rigorously optimized so that just about each transistor served a particular goal.

Freeman proposed a distinct strategy. He figured Moore’s Law would quickly change chip economics. The precept holds that transistor counts roughly double each two years, making computing cheaper and extra highly effective. Freeman posited that as transistors grew to become ample, flexibility would matter greater than excellent effectivity.

He envisioned a tool composed of programmable logic blocks linked via configurable routing—a chip stuffed with what he described as “open gates,” able to be outlined by customers after manufacturing. As a substitute of fixing {hardware} in silicon completely, engineers might configure and reconfigure circuits as necessities developed.

Freeman generally in contrast the idea to a clean cassette tape: Producers would provide the medium, whereas engineers decided its operate. The analogy captured a profound shift in who controls the know-how, shifting {hardware} design flexibility from chip fabrication services to the system designers themselves.

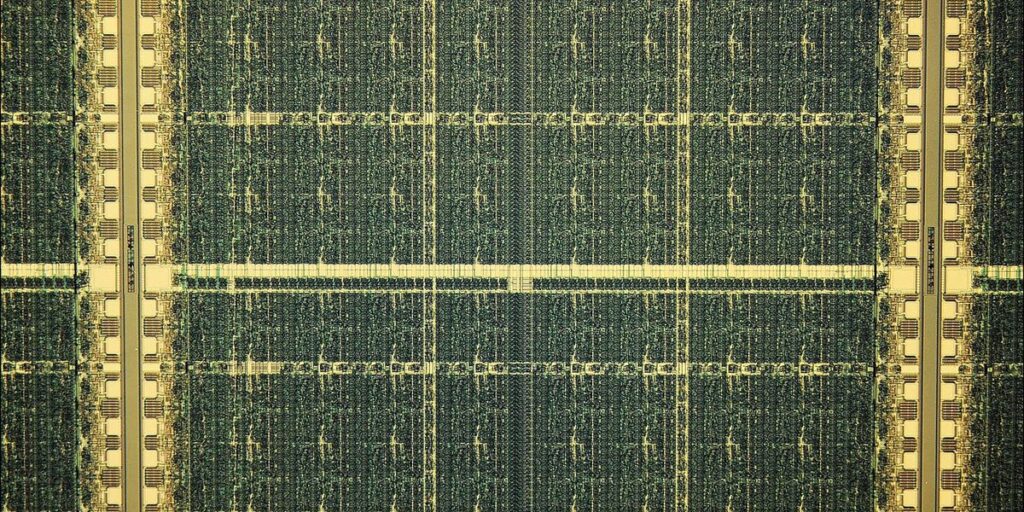

In 1985 Xilinx launched the primary FPGA for business sale: the XC2064. The machine contained 64 configurable logic blocks—small digital circuits able to performing logical operations—organized in an 8-by-8 grid. Programmable routing channels allowed engineers to outline how alerts moved between blocks, successfully wiring a customized circuit with software program.

Fabricated utilizing a 2-micrometer course of (that means that 2 µm was the minimal dimension of the options that may very well be patterned onto silicon utilizing photolithography), the XC2064 carried out just a few thousand logic gates. Fashionable FPGAs can comprise a whole bunch of tens of millions of gates, enabling vastly extra advanced designs. But the XC2064 established a design workflow nonetheless used in the present day: Engineers describe the {hardware} conduct digitally after which “compile the design,” a course of that robotically interprets the plans into the directions the FPGA must set its logic blocks and wiring, based on AMD. Engineers then load that configuration onto the chip.

The breakthrough: {hardware} outlined by reminiscence

Earlier programmable logic devices, similar to erasable programmable read-only reminiscence, or EPROM, allowed restricted customization however relied on largely mounted wiring constructions that did not scale well as circuits grew extra advanced, Cong says.

FPGAs launched programmable interconnects—networks of digital switches managed by reminiscence cells distributed throughout the chip. When powered on, the machine masses a bitstream configuration file that determines how its inner circuits behave.

“As course of know-how improved and transistor counts elevated, the price of programmability grew to become a lot much less vital,” Cong says.

From “glue logic” to important infrastructure

“Initially, FPGAs had been used as what engineers referred to as glue logic,” Cong says.

Glue logic refers to easy circuits that join processors, reminiscence, and peripheral units so the system works reliably, based on PC Magazine. In different phrases, it “glues” totally different parts collectively, particularly when interfaces change ceaselessly.

Early adopters acknowledged the benefit of {hardware} that might adapt as requirements developed. In “The History, Status, and Future of FPGAs,” revealed in Communications of the ACM, engineers at Xilinx and organizations similar to Bell Labs, Fairchild Semiconductor, IBM, and Sun Microsystems stated the earliest makes use of of FPGAs were for prototyping ASICs. In addition they used it for validating complex systems by working their software program earlier than fabrication, permitting the businesses to deploy specialised merchandise manufactured in modest volumes.

These makes use of revealed a broader shift: {Hardware} now not wanted to stay mounted as soon as deployed.

Attendees on the Milestone plaque dedication ceremony included (seated L to R) 2025 IEEE President Kathleen Kramer, 2024 IEEE President Tom Coughlin, and Santa Clara Valley Part Milestones Chair Brian Berg.Douglas Peck/AMD

Semiconductor economics modified the equation

The rise of FPGAs carefully adopted adjustments in semiconductor economics, Cong says.

Growing a customized chip requires a big upfront funding earlier than manufacturing begins. As fabrication prices elevated, merchandise needed to ship in massive portions to make ASIC growth economically viable, based on a post revealed by AnySilicon.

FPGAs allowed designers to maneuver ahead with out that bigger financial dedication.

ASIC growth usually requires 18 to 24 months from conception to silicon, whereas FPGA implementations usually will be accomplished inside three to 6 months utilizing fashionable design instruments, Cong says. The shorter cycle and the power to reconfigure the {hardware} enabled startups, universities, and gear producers to experiment with superior architectures that had been beforehand accessible primarily to massive chip corporations.

Lookup tables and the rise of reconfigurable computing

A well-liked method for implementing mathematical features in {hardware} isthe lookup table (LUT). A LUT is a small reminiscence component that shops the outcomes of logical operations, based on “LUT-LLM: Efficient Large Language Model Inference with Memory-based Computations on FPGAs,” a paper chosen for presentation subsequent month on the thirty fourth IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM).

As a substitute of repeatedly recalculating outcomes, the chip retrieves solutions instantly from reminiscence. Cong compares the strategy to consulting multiplication tables quite than recomputing the arithmetic every time.

Analysis led by Cong and others helped develop environment friendly strategies for mapping digital circuits onto LUT-based architectures, shaping routing and format methods utilized in fashionable units.

As transistor budgets expanded, FPGA distributors built-in reminiscence blocks, digital signal-processing items, high-speed communication interfaces, cryptographic engines, and embedded processors, reworking the units into versatile computing platforms.

Why the gate arrays are distinct from CPUs, GPUs, and ASICs

FPGAs coexist with different processors as a result of each optimizes totally different priorities. Central processing items excel at normal computing. Graphics processing items, designed to carry out many calculations concurrently, dominate massive parallel workloads similar to AI coaching. ASICs present most effectivity when designs stay secure and manufacturing volumes are excessive.

“ASICs can ship the perfect efficiency, however the growth cycle is lengthy, and the nonrecurring engineering price will be very excessive. FPGAs present a candy spot between processors and customized silicon.” —Jason Cong, IEEE Fellow and professor of laptop science at UCLA.

“FPGAs are usually not replacements for CPUs or GPUs,” Cong says. “They complement these processors in heterogeneous computing methods.”

Fashionable computing platforms more and more mix a number of kinds of processors to stability flexibility, efficiency, and energy efficiency.

A Milestone for an thought, not only a machine

This IEEE Milestone acknowledges greater than a profitable semiconductor product. It additionally acknowledges a shift in how engineers innovate.

Reconfigurable {hardware} permits designers to check concepts rapidly, refine architectures, and deploy methods whereas requirements and markets evolve.

“With out FPGAs,” Cong says, “the tempo of {hardware} innovation would doubtless be a lot slower.”

4 a long time after the primary FPGA appeared, the know-how’s enduring legacy displays Freeman’s perception: {Hardware} didn’t want to stay mounted. By accepting a small quantity of unused silicon in alternate for adaptability, engineers reworked chips from static merchandise into platforms for steady experimentation—turning silicon itself right into a medium engineers might rewrite.

Amongst those that attended the Milestone ceremony had been 2025 IEEE President Kathleen Kramer; 2024 IEEE President Tom Coughlin; Avery Lu, chair of the IEEE Santa Clara Valley Section; and Brian Berg, historical past and milestones chair of IEEE Region 6. They joined AMD’s chief government, Lisa Su, and Salil Raje, senior vice chairman and normal supervisor of adaptive and embedded computing at AMD.

The IEEE Milestone plaque honoring the field-programmable gate array reads:

“The FPGA is an built-in circuit with user-programmable Boolean logic features and interconnects. FPGA inventor Ross Freeman cofounded Xilinx to productize his 1984 invention, and in 1985 the XC2064 was launched with 64 programmable 4-input logic features. Xilinx’s FPGAs helped speed up a dramatic business shift whereby ‘fabless’ corporations might use software program instruments to design {hardware} whereas participating ‘foundry’ corporations to deal with the capital-intensive job of producing the software-defined {hardware}.”

Administered by the IEEE History Center and supported by donors, the IEEE Milestone program acknowledges excellent technical developments worldwide which are at the very least 25 years outdated.

Take a look at Spectrum’s History of Technology channel to learn extra tales about key engineering achievements.

From Your Website Articles

Associated Articles Across the Internet